# EE 435 Lecture 43

## Phased Locked Loops and VCOs

### Final Exam:

Scheduled on Final Exam Schedule:

```

Wednesday May 14 7:30 a.m.

```

Revised Final Exam:

- Take-home format open book and open notes

- Will be posted on course WEB site by Wednesday May 7

- Due at 9:30 a.m. on Wednesday May 14 : Provide hard copy and a backup solution as a pdf file in Canvas

- Honor system students must agree to not discuss the exam with anyone except the course instructor or TA, not post or distribute the exam to any third party, and not use any outside resources (such as Chegg) for solving any problems on the exam.

If anyone has any constraints that makes it difficult to work with this revised format or would like to do an in-person exam from 7:30 to 9:30 on May 14, please contact Professor Geiger by 5:00 p.m. on Wednesday May 7

# Bias Voltages/Currents Generators

How are these voltages and currents generated?

#### Voltage Outputs:

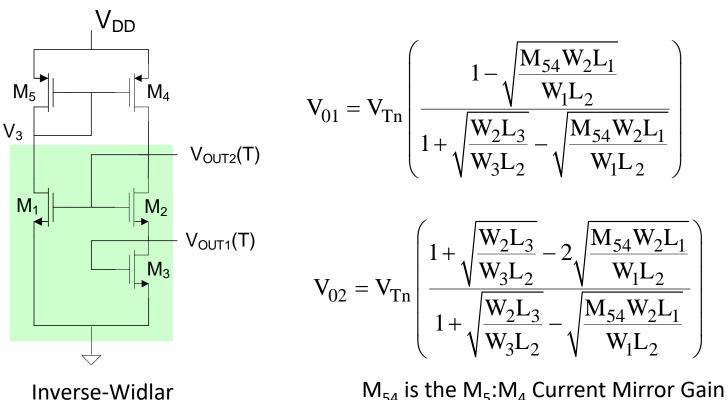

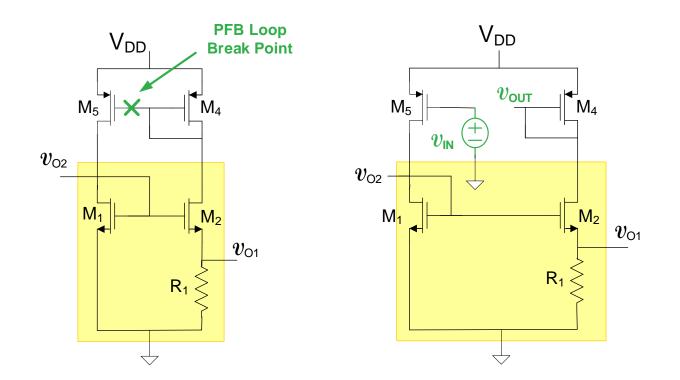

Supply-independent Bias Generator! Start-up circuit needed (notice positive feedback loop) Supply-independent Bias Generators Widely Used

#### **Review from last lecture**

### **Bias Voltages/Currents Generators**

Need for Start-up Circuit

$V_{OUT}=f(V_{IN})$  termed the return map

**Termed Homotopy Analysis**

Must not perturb operating point when breaking loop !

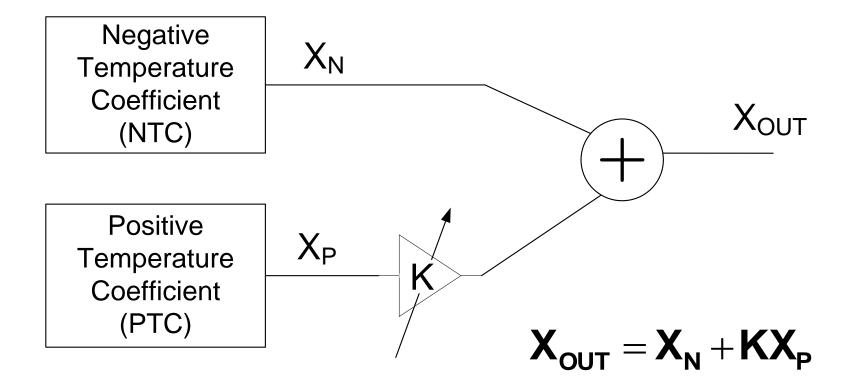

# Standard Approach to Building Voltage References

Pick K so that at some temperature  $T_0$ ,

$$\frac{\partial (\mathbf{X}_{N} + \mathbf{K} \mathbf{X}_{P})}{\partial \mathbf{T}} \bigg|_{\mathbf{T} = \mathbf{T}_{0}} = \mathbf{0}$$

**Review from last lecture**

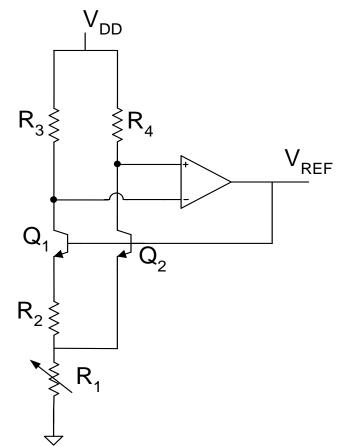

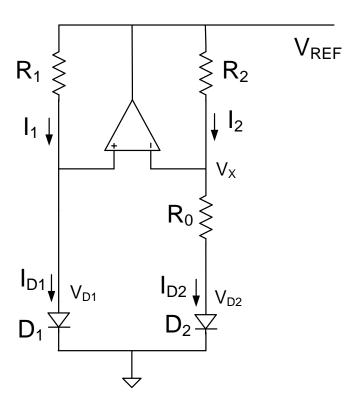

#### Early Bandgap Reference (and still widely used!)

P.Brokaw, "A Simple Three-Terminal IC Bandgap Reference", IEEE Journal of Solid State Circuits, Vol. 9, pp. 388-393, Dec. 1974.

- Brokaw coined term "bandgap reference" when referring to this circuit

- Properties very similar circuits introduced by Widlar and Kujik a small while earlier

- Paper submitted May 1974, Widlar paper submitted March 1970

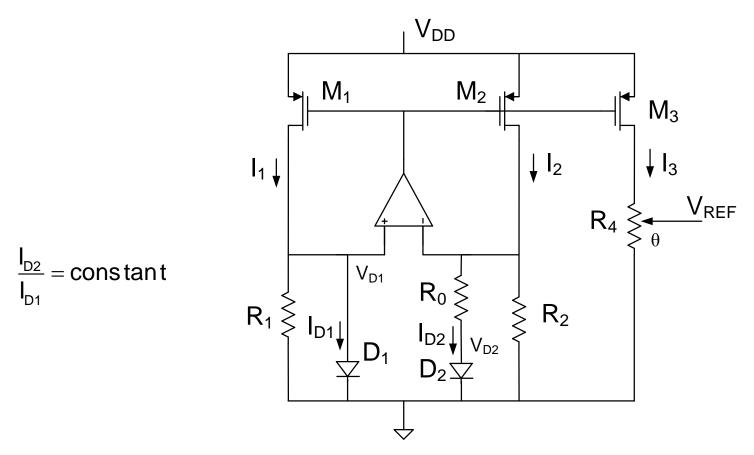

#### Review from last lecture Banba Bandgap Reference

[7] H. Banba, H. Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, A. Atsumi, and K. Sakkui, IEEE Journal of Solid-State Circuits, Vol. 34, pp. 670-674, May 1999.

Note this was introduced 25 years after the Brokaw reference

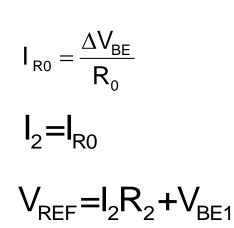

#### Review from last lecture Kujik Bandgap Reference

solving, we obtain

$$V_{\text{REF}} = \frac{R_2}{R_0} \Delta V_{\text{BE}} + V_{\text{BE1}}$$

$$V_{\text{REF}} = a_{22} + b_{22}T + c_{22}T \ln T$$

# First Bandgap Reference (and still widely used!)

#### Only 2mV change over 200°C temp range !

### **Injection Locking**

https://www.youtube.com/watch?v=W1TMZASCR-I

### Phase Locked Loops

Special case of injection-locked systems

In 1600's pendulums and organ pipes were occasionally injection locked

In 1919 electronic oscillators were observed that lock or sychronize

For the subsequent several decades, a form of PLLs was used to build radio and television receivers

In 1969 Signetics introduced the first integrated PLLs (NE 565 and NE 567)

In 1970's RCA introduced the 4046 PLL

### Phase Locked Loops

PLLs widely used throughout industry today

Easy to establish basic operation of a PLL

Highly nonlinear systems with seemingly simple operation but high-end designs can become quite complicated and mathematical rigor is often cumbersome and only approximate

Performance potential of most wireless communication systems and serial data transmission networks strongly dependent upon the performance characteristics of multiple embedded PLLs

Concepts of DLL and PLL are closely related

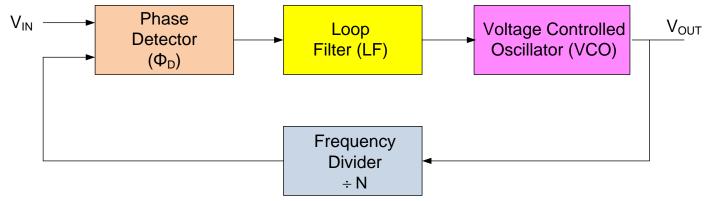

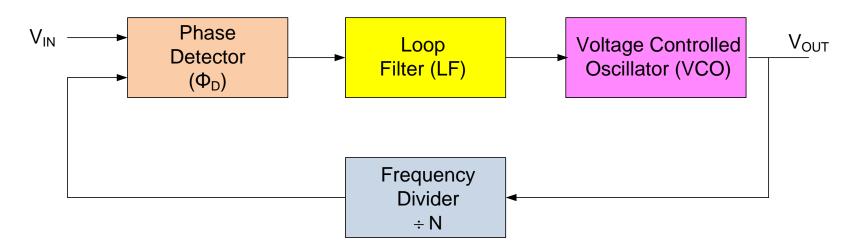

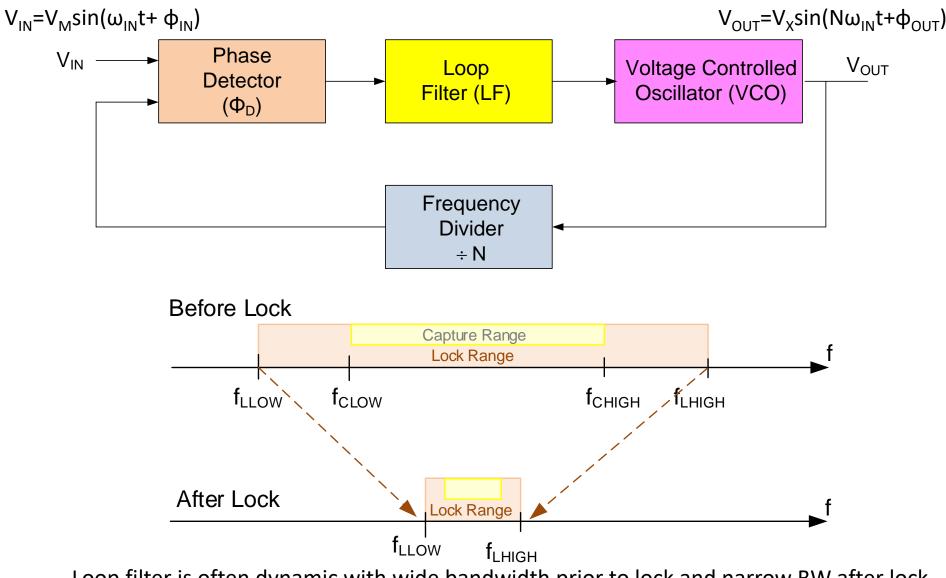

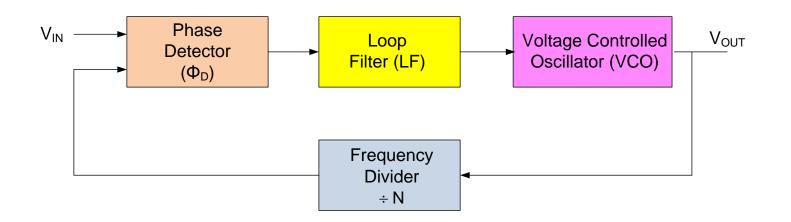

### **Basic PLL Architecture**

Applications include:

Frequency Demodulation Frequency Synthesis Clock Synchronization Noise filtering (extreme) Tracking and calibrated filters

- One of the most widely used analog blocks

- Many SoC systems include multiple PLLs

- Closely related to Delay Locked Loop (DLL)

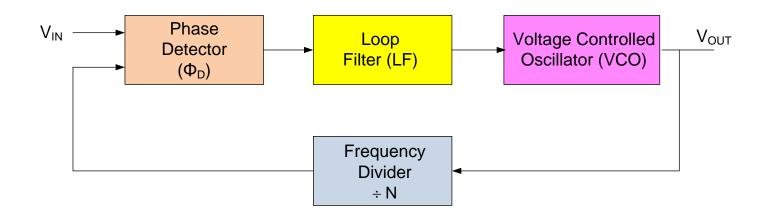

### **Basic PLL Architecture**

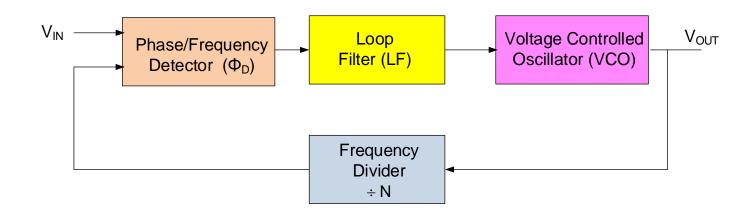

Most basic structure actually uses phase/frequency detector but still termed PLL<sup>1</sup>

<sup>1</sup>Ian Collins, "Phase-Locked Loop (PLL) Fundamentals", Analog Dialogue, July 2018.

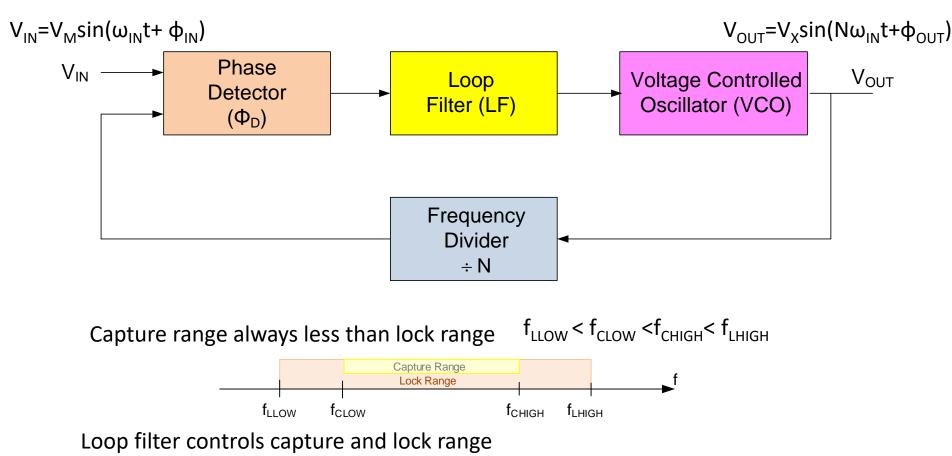

### **Basis PLL Architecture**

Applications by subcategory: Clock and Data Recovery Recovering signals when SNR <<<1 Timing generators in digital systems

$V_{IN}=V_{M}sin(\omega_{IN}t+\varphi_{IN})$

Desired output when locked:

$V_{OUT} = V_X sin(N\omega_{IN}t + \phi_{OUT})$

- Relationship between  $V_{\mathsf{M}}$  and  $V_{\mathsf{X}}$  is of little concern

- Frequency relationship is critical

- $\phi_{OUT}$  is often critical too

- Waveshape of V<sub>IN</sub> and V<sub>OUT</sub> is often of little concern May be highly distorted or even square waves

$V_{IN} = V_M sin(\omega_{IN}t + \phi_{IN})$

Desired output when locked:

$V_{OUT} = V_X sin(N\omega_{IN}t + \phi_{OUT})$

Some Terminology of PLLs

Locked / UnlockedLocked when  $V_{OUT}$  assumes desired valueLock RangeLocked when  $V_{OUT}$  assumes desired valueLock Range $f_{LLOW} < f_{IN} < f_{LHIGH}$ Capture Range $f_{CLOW} < f_{IN} < f_{CHIGH}$ Free-running frequency $f_{CLOW} < f_{IN} < f_{CHIGH}$ Harmonic/Subharmonic LockLocked when VOUT

Jitter in VCO output strongly dependent upon lock range

(large lock range results in high jitter, low lock range in low jitter)

Loop filter is often dynamic with wide bandwidth prior to lock and narrow BW after lock

Loop filter is often dynamic with wide bandwidth prior to lock and narrow BW after lock

#### Conceptual Operation of PLL

Consider a signal defined for  $-\infty < t < \infty$  expressed as

$V(t) = V_M sin(\phi(t))$

If the signal is sinusoidal with frequency  $\omega$ , the argument  $\phi$  can be expressed as

$\phi(t)=\omega t+\theta$

where  $\phi$  is defined to be the phase of the signal and  $\theta$  is the phase offset on the time axis from the time reference t=0

Taking the time derivative of  $\phi(t)$ , we obtain

$$\frac{d\phi}{dt} = \omega$$

Taking the Laplace Transform, we have

$$\phi_{\rm S} = \frac{\omega}{\rm S}$$

Is the second statement "If the signal is sinusoidal ...." redundant ?

#### Is the second statement "If the signal is sinusoidal ...." redundant ?

Consider a signal defined for  $-\infty < t < \infty$  expressed as

$V(t) = V_M sin(\phi)$

If the signal is sinusoidal with frequency  $\omega$ , the argument  $\phi$  can be expressed as

$\phi = \omega t + \theta$

Consider any signal f(t) defined for all time (not necessarily periodic but could be)

Define  $\phi(t)$  by the expression  $\phi(t) = \sin^{-1}\left(\frac{f(t)}{V_M}\right)$

It follows that

$$V(t) = V_{M} \sin(\phi(t)) = V_{M} \sin\left(\sin^{-1}\left(\frac{f(t)}{V_{M}}\right)\right) = f(t)$$

Thus, the first statement gives NO information about the signal V(t)

### Consider a VCO where the output is sinusoidal

Assume the output of interest is the phase  $\phi$

$$V_{LF} \qquad Voltage Controlled \\ Oscillator (VCO) \qquad \Phi \quad V_{OUT} \\ \varphi(t) = \omega t + \theta \\ V_{OUT} = V_m \sin(\omega t + \theta) \\ \omega = V_{LF} \bullet K_{VCO} \\ \frac{d\phi}{dt} = \omega = V_{LF} K_{VCO} \\ \frac{d\phi}{dt} = \omega = V_{LF} K_{VCO} \\ Taking Laplace Transform: S\phi_S = V_{LFS} K_{VCO} \qquad \longrightarrow \qquad \phi_S = V_{LFS} \frac{K_{VCO}}{S} \\ V_{LFS} \qquad K_{VCO} \qquad \Phi_S = V_{LFS} \frac{K_{VCO}}{S} \\ V_{CO} \qquad V_{OUT} \\ V_{CO} \qquad V_{CO} \\ V_{CO} \\ V_{CO} \\ V_{CO} \\ V_{CO} \\ V_{CO} \\ V_{CO}$$

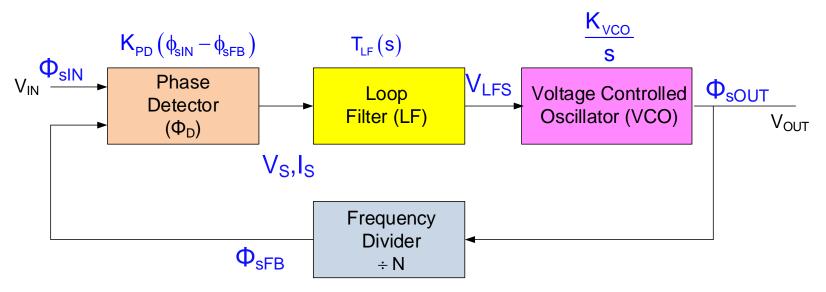

#### Conceptual Operation of PLL

- When locked, PLL can be modeled as a linear system

- Small-signal s-domain analysis when PLL is locked

Note: Dimensions of variables in loop are not the same

$$V_{S} = K_{PD} (\phi_{SIN} - \phi_{SFB})$$

$$V_{LFS} = T_{LF} (s) V_{S}$$

$$\phi_{SOUT} = V_{LFS} \frac{K_{VCO}}{s}$$

$$f_{PLL} (s) = \frac{\phi_{SOUT}}{\phi_{SIN}} = \frac{T_{LF} (s) K_{PD} K_{VCO}}{s + T_{LF} (s) \frac{K_{VCO} K_{PD}}{N}}$$

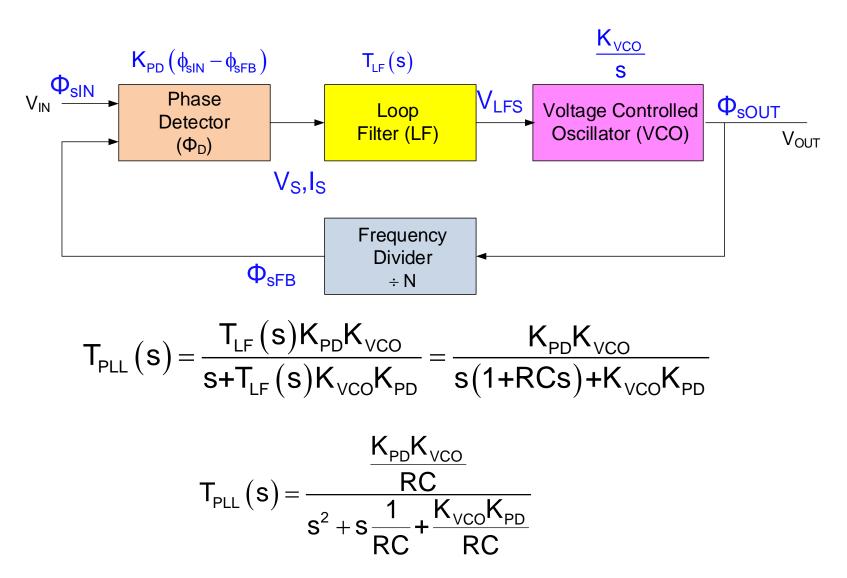

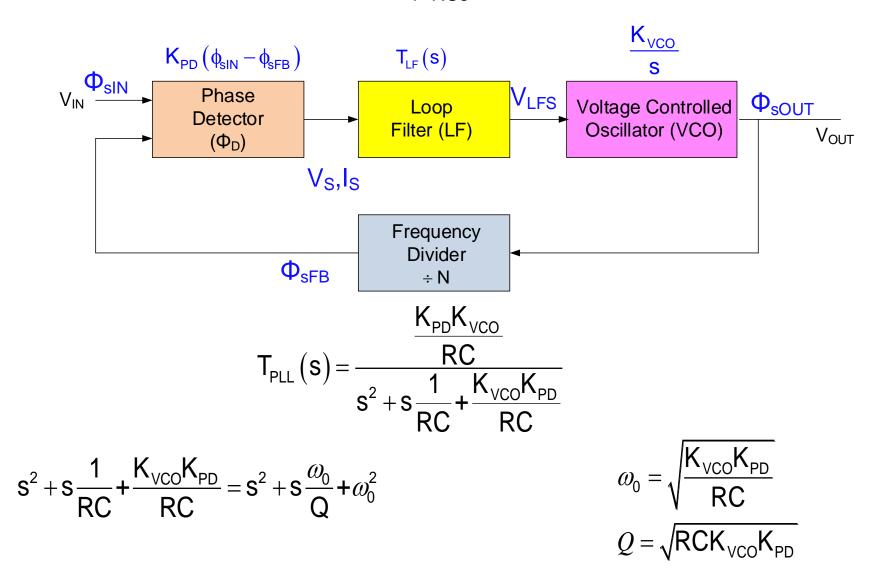

#### Often the LF is low order

Example: Assume N=1 and  $T_{LF}(s) = \frac{1}{1+RCs}$

#### Often the LF is low order

Example: Assume N=1 and  $T_{LF}(s) = \frac{1}{1+RCs}$

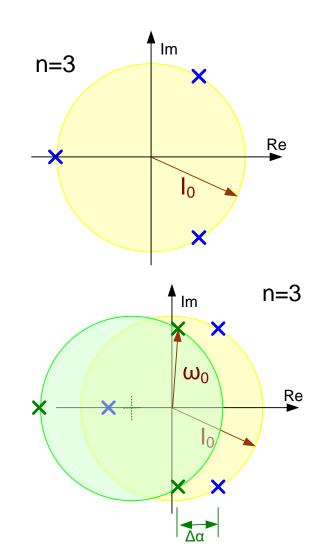

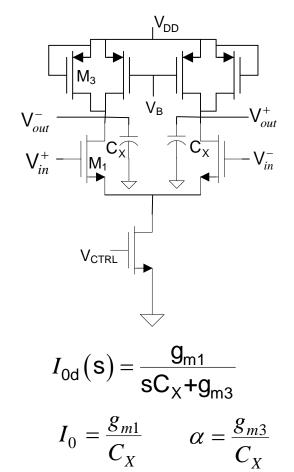

### Voltage Controlled Oscillators

#### Many different VCOs can be used

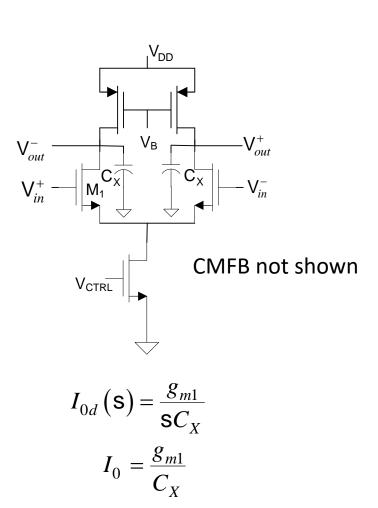

Assume  $I_0$  is determined by a controlling voltage

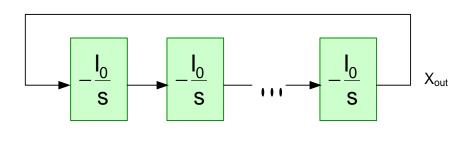

Integrator-Based VCO

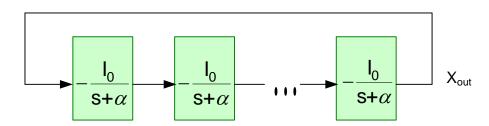

Lossy Integrator-Based VCO

#### Voltage Controlled Oscillator (VCO)

**Voltage Controlled Oscillators**

Integrator for: Integrator-based VCO

Voltage Controlled Oscillator (VCO)

Integrator for: Lossy Integrator-based VCO

#### **Voltage Controlled Oscillators**

#### Voltage Controlled Oscillator (VCO)

#### Relaxation Oscillator Derived VCO (comparator not Op Amp)

R  $V_{Z}$ R -∕∕//-ላላሌ V<sub>OUT</sub> VOUT С С ₩ R<sub>2</sub> R<sub>1</sub> VOUT  $M_2$ 々 -V<sub>X</sub>  $V_X$  $V_Z$ VSATH Vx  $V_{\mathsf{SATL}}$

$V_z$  is approximately triangle wave,  $V_{OUT}$  is square wave

Can have either triangle wave or square wave ouputs

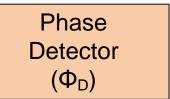

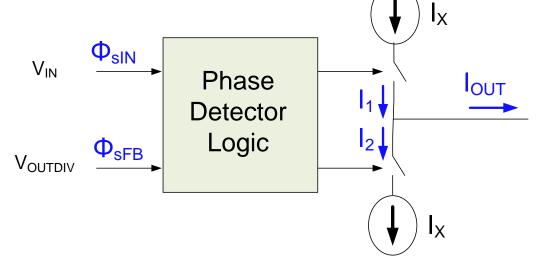

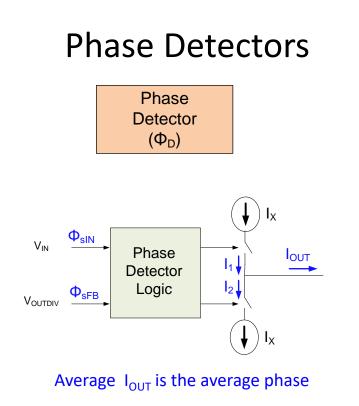

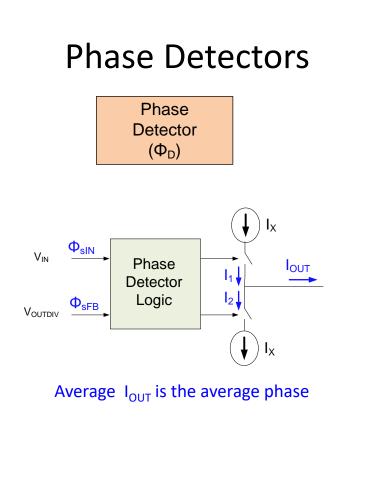

#### **Phase Detectors**

#### Many different Phase Detectors can be used

Some Popular Phase Detector Circuits Analog Multiplier Exclusive OR Gate Sample and Hold Charge Pump

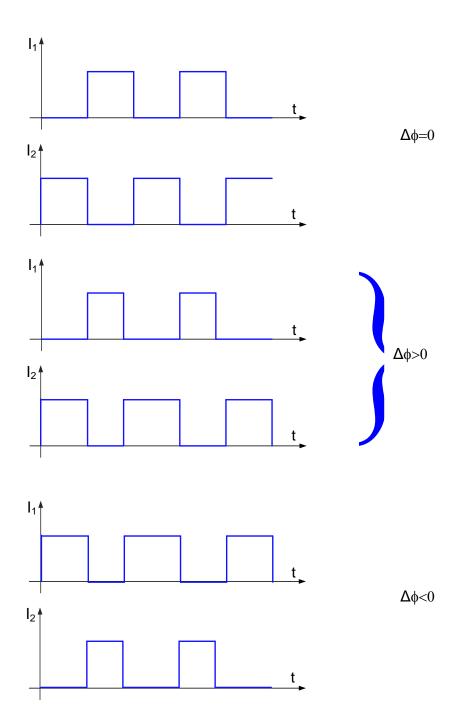

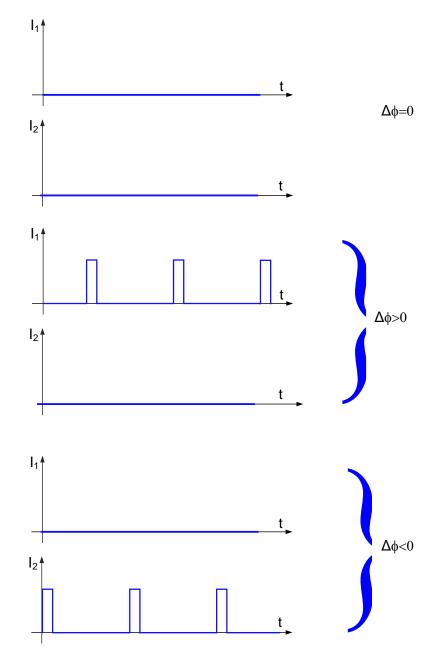

Charge-pump based Phase Detector

Average  $I_{OUT}$  is the average phase

#### **Phase Detectors**

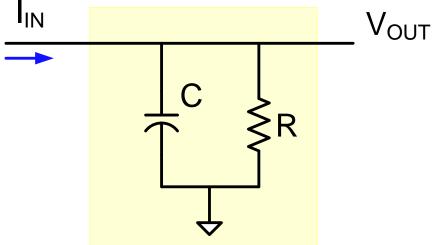

#### Many different Phase Detectors can be used

Desired phase difference often 0° or 90°

Phase

Detector

$(\Phi_D)$

Vulnerable to dead zone problem

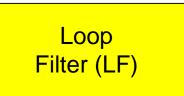

#### **Loop Filters**

Many different Phase Detectors can be used Often the loop filter is first or second order Usually the loop filter circuit is very simple

#### $T_{LF}(s)$

$\frac{V_{OUT}}{I_{INAVG}} = T_{LF}(s) = \frac{R}{1 + RCs}$

Basic first-order LF with average current difference as input

#### What is the phase of a signal?

Assume  $\omega_1 = \omega_2 = \omega$

If V<sub>1</sub> can be expressed as  $V_1 = V_{M1} \sin(\omega t + \phi_1)$  the phase is  $\phi_1$

But what is the phase if  $\omega$  is time varying? Or what is the "phase" if this functional form does not really characterize V(t)? Or what if  $\omega_1 \neq \omega_2$ ?

What does a phase detector do if the two inputs are not at the same frequency?

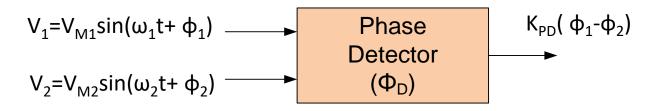

#### What is the phase of a signal?

Most Phase Detectors are actually Phase/Frequency Detectors

- Large output when frequency difference exists

- Also provides output when phase difference exists after frequencies are matched

#### **Phase-Locked Loops**

- Phase-Locked Loops are Widely Used

- Applications span extremely wide range of frequencies

- Invariably substantial nonlinearity complicating exact analysis

- Conceptual linear analysis gives considerable insight into operation

- Computer simulations used to mitigate nonlinarity analysis challenges

# Stay Safe and Stay Healthy !

# End of Lecture 43